Innovación Japonesa en la Fabricación de Chips Avanzados

Contexto de la Industria de Semiconductores

La fabricación de semiconductores representa uno de los pilares fundamentales de la economía digital global. Los chips de silicio, esenciales para dispositivos electrónicos como smartphones, computadoras y sistemas de inteligencia artificial, se producen mediante procesos complejos que involucran litografía extrema ultravioleta (EUV) y equipos de alta precisión. Tradicionalmente, la producción de nodos avanzados, como los de 1-4 nanómetros (nm), ha estado limitada a unas pocas naciones con infraestructuras avanzadas, como Taiwán, Corea del Sur y Estados Unidos. Esta concentración genera vulnerabilidades en la cadena de suministro y excluye a países en desarrollo de participar en este sector estratégico.

En este escenario, Japón ha emergido con un avance tecnológico que democratiza el acceso a la manufactura de chips de alta densidad. Esta innovación busca reducir las barreras económicas y técnicas, permitiendo que naciones con recursos limitados incorporen la producción local de semiconductores avanzados sin depender de importaciones costosas.

Descripción Técnica de la Nueva Tecnología

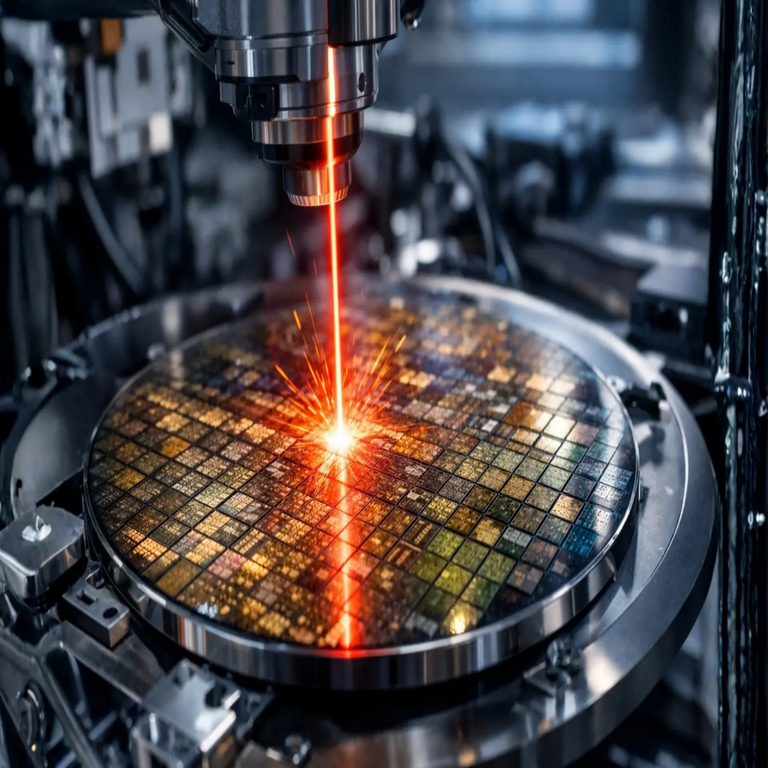

La tecnología desarrollada por investigadores japoneses se centra en un método innovador de litografía y deposición de capas que optimiza el proceso de fabricación de transistores en escalas nanométricas. A diferencia de los enfoques convencionales, que requieren máquinas EUV de millones de dólares y entornos de sala limpia ultraesterilizados, esta solución emplea técnicas de autoensamblaje molecular y patrones inducidos por luz visible o ultravioleta convencional.

El núcleo del proceso involucra la utilización de polímeros dirigidos por autoensamblaje (DSA, por sus siglas en inglés), que permiten la creación de patrones finos sin necesidad de longitudes de onda extremadamente cortas. En nodos de 1-4 nm, los transistores FinFET o GAA (Gate-All-Around) se benefician de esta aproximación al reducir la variabilidad en la alineación de capas, minimizando defectos y aumentando el rendimiento por unidad de área.

- Autoensamblaje molecular: Moléculas orgánicas se organizan espontáneamente en estructuras periódicas, guiadas por interacciones químicas, para formar máscaras de litografía con resoluciones inferiores a 5 nm.

- Depósito selectivo de área: Técnicas de deposición química en vapor (CVD) selectiva permiten el crecimiento preciso de materiales como el silicio o germanio solo en regiones predefinidas, evitando pasos de grabado agresivos que generan residuos.

- Integración con procesos existentes: Compatible con líneas de producción legacy, esta tecnología requiere inversiones iniciales hasta un 70% menores en comparación con EUV, según estimaciones preliminares.

Los experimentos realizados en laboratorios japoneses han demostrado una densidad de transistores superior a 100 millones por milímetro cuadrado, comparable a estándares industriales actuales, pero con un consumo energético reducido en la fase de fabricación.

Beneficios para Países en Desarrollo

Esta innovación tiene implicaciones profundas para economías emergentes. Países como aquellos en América Latina, África o el sudeste asiático, que carecen de acceso a tecnologías de punta, podrían establecer fábricas de semiconductores locales con costos iniciales accesibles. Por ejemplo, la producción de chips de 4 nm para aplicaciones en IoT (Internet de las Cosas) o edge computing se vuelve viable sin alianzas exclusivas con gigantes como TSMC o Intel.

Entre los beneficios clave se destacan:

- Reducción de dependencia geopolítica: Menos vulnerabilidad a interrupciones en la cadena de suministro global, como las observadas durante la pandemia de COVID-19 o tensiones comerciales.

- Estímulo económico: Creación de empleos en ingeniería y manufactura, fomentando la transferencia de conocimiento y el desarrollo de ecosistemas tecnológicos locales.

- Sostenibilidad ambiental: El proceso consume menos agua y energía, alineándose con objetivos de desarrollo sostenible al minimizar el impacto ecológico de la producción de silicio.

Además, esta tecnología podría integrarse con avances en blockchain para rastrear la autenticidad de chips producidos, asegurando la integridad en aplicaciones de ciberseguridad e IA distribuida.

Desafíos y Consideraciones Técnicas

A pesar de sus promesas, la adopción enfrenta obstáculos. La escalabilidad a producción masiva requiere validaciones adicionales en cuanto a tasas de rendimiento (yield) y confiabilidad a largo plazo. En nodos sub-2 nm, fenómenos cuánticos como el túnel de electrones podrían demandar refinamientos en los materiales, posiblemente incorporando compuestos bidimensionales como el grafeno o el nitruro de boro.

Otro aspecto crítico es la protección de propiedad intelectual. Japón, a través de instituciones como la Universidad de Tokio y empresas como Tokyo Electron, debe equilibrar la difusión tecnológica con salvaguardas contra usos indebidos en contextos de ciberseguridad.

Perspectivas Futuras y Cierre

Esta innovación japonesa marca un punto de inflexión en la democratización de la tecnología de semiconductores, potenciando la inclusión de países en desarrollo en la era de la computación cuántica e IA. Al facilitar la producción local de chips avanzados, se promueve una economía global más equitativa y resiliente. Futuras colaboraciones internacionales podrían acelerar su implementación, transformando desafíos en oportunidades para el avance tecnológico colectivo.

Para más información visita la Fuente original.