Más allá de Von Neumann: Hacia una arquitectura unificada y determinista en la computación e inteligencia artificial

Introducción a la arquitectura de Von Neumann y sus fundamentos

La arquitectura de Von Neumann, propuesta por John von Neumann en la década de 1940, ha sido el pilar fundamental de la computación digital moderna. Esta arquitectura se caracteriza por la separación estricta entre el procesador (unidad central de procesamiento o CPU) y la memoria, donde las instrucciones y los datos se almacenan en la misma unidad de memoria y se acceden secuencialmente a través de un bus de datos. Este modelo ha permitido el desarrollo de computadoras programables de propósito general, desde las primeras máquinas electrónicas hasta los sistemas actuales de alto rendimiento.

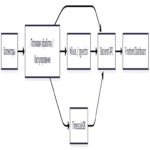

En términos técnicos, la arquitectura de Von Neumann opera bajo un ciclo de fetch-decode-execute: el procesador recupera una instrucción de la memoria (fetch), la decodifica para entender la operación requerida y luego la ejecuta, potencialmente accediendo a datos adicionales en la memoria. Esta separación, aunque eficiente para tareas secuenciales, introduce latencias inherentes debido al cuello de botella de Von Neumann, donde el ancho de banda limitado del bus entre la CPU y la memoria restringe el rendimiento en aplicaciones que demandan procesamiento paralelo masivo.

En el contexto de la inteligencia artificial (IA) y el aprendizaje automático, esta arquitectura ha sido adaptada mediante extensiones como las unidades de procesamiento gráfico (GPU) y los aceleradores de IA específicos, como los tensor processing units (TPU) de Google. Sin embargo, estas adaptaciones mantienen la dicotomía memoria-procesamiento, lo que genera ineficiencias energéticas y de escalabilidad en modelos de IA grandes, como las redes neuronales profundas que requieren terabytes de datos para el entrenamiento.

Limitaciones de la arquitectura de Von Neumann en la era de la IA

Una de las principales limitaciones de la arquitectura de Von Neumann radica en su enfoque secuencial, que no se alinea óptimamente con las demandas de la computación paralela inherente a la IA. En el entrenamiento de modelos de machine learning, por ejemplo, las operaciones matriciales y vectoriales deben realizarse en paralelo, pero el constante movimiento de datos entre la memoria y el procesador consume una porción significativa de la energía total, estimada en hasta el 90% en algunos sistemas neuromórficos emergentes.

Desde una perspectiva energética, la ley de Moore, que predice el duplicado de transistores cada dos años, se está agotando debido a límites físicos en la miniaturización de semiconductores. Esto agrava el problema del cuello de botella de Von Neumann, ya que el aumento en la densidad de transistores no se traduce directamente en mejoras en el ancho de banda de memoria. Estudios de la industria, como los reportados por la IEEE, indican que el consumo energético de los centros de datos para IA podría superar el 8% del consumo global de electricidad para 2030 si no se abordan estas ineficiencias.

Adicionalmente, la arquitectura de Von Neumann es inherentemente probabilística en su ejecución debido a factores como el pipelining, el caching y las interrupciones, lo que complica la implementación de sistemas deterministas requeridos en aplicaciones críticas de IA, tales como la conducción autónoma o el control de sistemas médicos. En estos escenarios, la reproducibilidad exacta de resultados es esencial para la verificación y validación, pero el modelo actual introduce variabilidad no deseada.

En el ámbito de la ciberseguridad, estas limitaciones exponen vulnerabilidades. El constante flujo de datos entre memoria y procesador facilita ataques de side-channel, como Spectre y Meltdown, que explotan el comportamiento especulativo de los procesadores para extraer información sensible. Una arquitectura más unificada podría mitigar estos riesgos al reducir las superficies de ataque asociadas al movimiento de datos.

Hacia una arquitectura unificada: Integrando memoria y procesamiento

La transición más allá de Von Neumann implica el desarrollo de arquitecturas unificadas, donde la memoria y el procesamiento se integran en un sustrato común, inspirado en modelos biológicos como el cerebro humano. En el cerebro, los sinapsis actúan tanto como almacenamiento de información como sitios de cómputo, permitiendo un procesamiento paralelo y eficiente sin un cuello de botella centralizado.

Una aproximación clave es la computación en memoria (in-memory computing), donde las operaciones lógicas se realizan directamente en las celdas de memoria, eliminando la necesidad de transferir datos. Tecnologías como las memorias de cambio de fase (PCM) y las memorias resistivas (ReRAM) permiten esto al modular la resistencia eléctrica para representar y computar bits. Por ejemplo, en un array de ReRAM, las multiplicaciones matriciales para redes neuronales pueden realizarse mediante la ley de Ohm, donde la corriente resultante representa el producto escalar sin mover datos.

Otro avance es la computación neuromórfica, ejemplificada por chips como el Intel Loihi o el IBM TrueNorth. Estos sistemas emulan spiking neural networks (SNN), donde los eventos neuronales se propagan asincrónicamente, reduciendo el consumo energético en órdenes de magnitud comparado con GPUs tradicionales. En Loihi, por instancia, el procesamiento se distribuye en núcleos que integran memoria local, permitiendo un paralelismo masivo con un consumo de menos de 1 watt por núcleo en tareas de inferencia de IA.

Desde el punto de vista de los protocolos y estándares, iniciativas como el Open Neuromorphic Standard de la Comunidad Internacional de Computación Neuromórfica promueven interfaces unificadas para hardware y software, facilitando la interoperabilidad. Esto incluye protocolos para el enrutamiento de spikes en redes neuromórficas, similares a paquetes IP en redes tradicionales, pero optimizados para eventos dispersos.

El determinismo en arquitecturas unificadas: Implicaciones técnicas

El determinismo se refiere a la propiedad de un sistema donde un estado inicial y una secuencia de entradas producen siempre el mismo estado final y salida, sin variabilidad estocástica. En la arquitectura de Von Neumann, el determinismo se ve comprometido por mecanismos como el reordenamiento out-of-order y el branching predictivo, que introducen no-determinismo para optimizar el rendimiento.

En una arquitectura unificada y determinista, se busca eliminar estas fuentes de variabilidad mediante diseños síncronos o asíncronos estrictos. Por ejemplo, en sistemas basados en lógica temporal, como los finite state machines (FSM) distribuidos en memoria, cada transición se define de manera determinista por reglas fijas, asegurando reproducibilidad. Esto es crucial para la IA explicable, donde modelos como las redes generativas antagónicas (GAN) requieren entrenamiento determinista para auditorías regulatorias.

Técnicamente, el logro del determinismo implica el uso de semillas fijas en generadores de números pseudoaleatorios (PRNG) y la sincronización global en sistemas distribuidos. En blockchain, por analogía, el consenso determinista (como en Proof-of-Stake mejorado) podría integrarse con arquitecturas unificadas para aplicaciones de IA descentralizada, asegurando que nodos en una red reproduzcan resultados idénticos sin bifurcaciones.

Los riesgos operativos incluyen el aumento en la complejidad de diseño, donde errores en la integración memoria-procesamiento podrían llevar a fallos catastróficos en sistemas embebidos. Beneficios, sin embargo, abarcan una reducción drástica en latencia: prototipos de computación fotónica unificada han demostrado latencias sub-nanosegundo en operaciones de IA, comparado con microsegundos en Von Neumann.

Tecnologías emergentes y marcos de trabajo para la implementación

Entre las tecnologías emergentes, la computación cuántica ofrece un paradigma unificado, donde qubits actúan como memoria y procesador simultáneamente mediante superposiciones. Frameworks como Qiskit de IBM permiten simular arquitecturas híbridas cuántico-clásicas, integrando determinismo en algoritmos como el variational quantum eigensolver (VQE) para optimización en IA.

En el ámbito de la IA, bibliotecas como TensorFlow y PyTorch están evolucionando hacia soporte para hardware unificado. Por ejemplo, la extensión de TensorFlow para neuromórficos permite mapear grafos de cómputo directamente a chips como Loihi, optimizando el despliegue de modelos convolucionales en entornos de bajo poder.

Para blockchain e IT, arquitecturas unificadas podrían habilitar smart contracts deterministas en redes como Ethereum 2.0, donde el procesamiento en memoria reduce el gas consumption en transacciones de IA on-chain. Herramientas como Solidity con extensiones para computación en memoria facilitan esto, asegurando ejecuciones verificables.

En ciberseguridad, estándares como NIST SP 800-53 recomiendan arquitecturas deterministas para sistemas de control industrial (ICS), donde la integración unificada mitiga ataques de denegación de servicio al minimizar dependencias en buses externos.

- Computación en memoria: Utiliza dispositivos no volátiles como PCM para operaciones in-situ, reduciendo el consumo energético en un 1000x para inferencia de IA.

- Neuromórficos: Chips con miles de núcleos que emulan plasticidad sináptica, ideales para edge computing en IoT.

- Fotónica y óptica integrada: Integra waveguides en silicio para procesamiento paralelo, con tasas de datos en Tbps sin latencia térmica.

- Computación cuántica híbrida: Combina qubits con memoria clásica unificada para algoritmos de machine learning cuántico (QCML).

Implicaciones operativas y regulatorias

Operativamente, la adopción de arquitecturas unificadas requiere una reingeniería de flujos de trabajo en centros de datos. Empresas como NVIDIA y AMD están invirtiendo en chips de memoria computacional, como las GPU con HBM3 (High Bandwidth Memory 3), que acercan la unificación al reducir distancias físicas entre memoria y núcleos.

Regulatoriamente, marcos como el GDPR en Europa exigen determinismo en procesamiento de datos de IA para garantizar privacidad. Una arquitectura unificada facilita el cumplimiento al permitir auditorías en tiempo real de flujos de datos in-situ, reduciendo el riesgo de fugas.

En términos de riesgos, la dependencia en tecnologías emergentes como ReRAM introduce vulnerabilidades a fallos por radiación cósmica, requiriendo redundancia y corrección de errores (ECC) avanzada. Beneficios incluyen escalabilidad: se proyecta que sistemas unificados alcancen exaFLOPS con consumos sub-kilowatt, habilitando IA distribuida en dispositivos móviles.

En blockchain, la integración con arquitecturas deterministas podría resolver el trilema de escalabilidad, seguridad y descentralización, permitiendo validación paralela de transacciones en memoria compartida sin consenso centralizado.

Casos de estudio y aplicaciones prácticas

Un caso emblemático es el proyecto de la DARPA SyNAPSE, que desarrolló chips neuromórficos para visión computacional, demostrando un 100x de eficiencia en reconocimiento de imágenes comparado con Von Neumann. En aplicaciones reales, estos chips se usan en drones autónomos para procesamiento en tiempo real sin conexión a la nube.

Otro ejemplo es el uso de computación en memoria en centros de datos de Google, donde TPUs v4 integran elementos de unificación para entrenamiento de modelos como PaLM, reduciendo tiempos de entrenamiento de semanas a días.

En ciberseguridad, prototipos de firewalls neuromórficos detectan anomalías en tráfico de red mediante patrones spiking, con tasas de falsos positivos inferiores al 0.1%, superando métodos basados en reglas tradicionales.

Para IT empresarial, arquitecturas unificadas habilitan virtualización de hardware determinista, donde contenedores de IA se ejecutan en pools de memoria compartida, optimizando recursos en entornos cloud híbridos.

Desafíos en la transición y estrategias de mitigación

Los desafíos incluyen la compatibilidad con software legacy, que asume la separación Von Neumann. Estrategias de mitigación involucran emuladores híbridos, como el framework NEST para simulación neuromórfica en CPUs estándar.

Otro reto es la fiabilidad: memorias no volátiles sufren desgaste por ciclos de escritura, limitando su vida útil a 10^6 operaciones. Soluciones como wear-leveling algoritmos, similares a SSDs, extienden esto a 10^12.

En términos de estándares, la falta de uniformidad entre proveedores (e.g., ARM vs. RISC-V en neuromórficos) requiere esfuerzos de estandarización por organizaciones como Khronos Group, que extienden OpenCL para computación unificada.

Finalmente, la educación y capacitación son esenciales; programas universitarios en computación post-Von Neumann, como los de MIT, preparan ingenieros para estos paradigmas.

Conclusión: El futuro de la computación unificada y determinista

La evolución más allá de la arquitectura de Von Neumann hacia modelos unificados y deterministas representa un cambio paradigmático en la computación e IA, abordando ineficiencias energéticas, latencias y vulnerabilidades inherentes al modelo actual. Al integrar memoria y procesamiento en sustratos innovadores como neuromórficos y en-memoria, se habilitan aplicaciones de IA escalables, seguras y eficientes, con implicaciones profundas en ciberseguridad, blockchain y sistemas IT.

Si bien persisten desafíos en implementación y estandarización, los avances tecnológicos y regulatorios pavimentan el camino para una adopción generalizada. En resumen, esta transición no solo optimiza el rendimiento, sino que redefine los límites de la innovación computacional, prometiendo un ecosistema donde la IA opera con precisión determinista y eficiencia biológica.

Para más información, visita la fuente original.