Samsung Retoma el Liderazgo en el Mercado de Memorias DRAM, Desplazando a SK Hynix

Introducción al Mercado de Memorias DRAM

Las memorias dinámicas de acceso aleatorio (DRAM, por sus siglas en inglés) representan un componente fundamental en la arquitectura de los sistemas informáticos modernos. Estas memorias se utilizan para almacenar datos de manera temporal y de alta velocidad, permitiendo el procesamiento eficiente en procesadores centrales, gráficos y sistemas embebidos. En el contexto de la industria tecnológica, el mercado de DRAM ha experimentado una evolución constante, impulsada por la demanda creciente de centros de datos, inteligencia artificial (IA) y dispositivos móviles. Recientemente, Samsung Electronics ha anunciado avances que le permiten recuperar la posición dominante en este sector, superando a su principal competidor, SK Hynix. Este cambio en la dinámica del mercado no solo refleja innovaciones en procesos de fabricación, sino también estrategias de producción y respuestas a las fluctuaciones económicas globales.

El mercado de DRAM se mide típicamente en términos de cuota de mercado por ingresos y capacidad de producción. Según datos de la industria, el segmento de DRAM generó aproximadamente 25 mil millones de dólares en 2023, con proyecciones de crecimiento anual compuesto del 10% hasta 2028, impulsado por la adopción de tecnologías de alto ancho de banda como HBM (High Bandwidth Memory) y DDR5. Samsung, como uno de los tres principales fabricantes junto con SK Hynix y Micron, ha invertido fuertemente en investigación y desarrollo para optimizar la densidad y el rendimiento de sus chips. Este artículo analiza los aspectos técnicos detrás de esta recuperación, las implicaciones para la cadena de suministro global y las oportunidades en aplicaciones emergentes como la IA y el blockchain.

Evolución Histórica del Mercado de DRAM

La historia del mercado de DRAM se remonta a la década de 1970, cuando Intel introdujo el primer chip DRAM comercial. Desde entonces, la tecnología ha avanzado a través de generaciones definidas por estándares como DDR (Double Data Rate), SDRAM (Synchronous DRAM) y más recientemente DDR4 y DDR5. Estos estándares, establecidos por la JEDEC Solid State Technology Association, especifican parámetros clave como la velocidad de transferencia de datos (medida en MT/s, megatransferencias por segundo), el voltaje operativo y la latencia CAS (Column Address Strobe).

En las últimas dos décadas, el mercado ha sido dominado por un oligopolio coreano-estadounidense. SK Hynix asumió el liderazgo en 2022, gracias a su enfoque en memorias HBM para GPUs de IA, como las utilizadas en los aceleradores de NVIDIA. Sin embargo, Samsung ha respondido con una estrategia agresiva de expansión de capacidad. En 2023, Samsung aumentó su producción de wafers en un 20%, utilizando litografía extrema ultravioleta (EUV) para fabricar chips en nodos de 1z nm (1 zeta nanómetros), que permiten una densidad de transistores superior al 30% comparado con procesos de 1α nm. Esta transición técnica reduce el consumo energético y mejora la eficiencia térmica, aspectos críticos para servidores de alto rendimiento.

Los datos de TrendForce indican que, en el primer trimestre de 2024, la cuota de mercado de Samsung en DRAM alcanzó el 43,5%, superando el 42,1% de SK Hynix. Este desplazamiento se atribuye a la recuperación post-pandemia y a la demanda de módulos DDR5 para plataformas de computación en la nube. Técnicamente, los chips DDR5 de Samsung operan a velocidades de hasta 8.400 MT/s, con una arquitectura de doble canal que duplica el ancho de banda en comparación con DDR4, alcanzando picos de 128 GB/s por módulo.

Avances Tecnológicos en los Chips DRAM de Samsung

Samsung ha invertido más de 20 mil millones de dólares en instalaciones de fabricación en Corea del Sur y Estados Unidos, enfocándose en la integración de tecnologías de vanguardia. Uno de los pilares de su estrategia es el desarrollo de memorias 3D DRAM, donde las celdas de memoria se apilan verticalmente para aumentar la densidad sin expandir el área de silicio. En contraste con las memorias 2D planas, esta aproximación utiliza técnicas de stacking como TSV (Through-Silicon Via), que permiten interconexiones verticales con una resistencia eléctrica inferior al 10% de las tradicionales wire-bonding.

En el ámbito de las memorias de alto rendimiento, Samsung lidera en HBM3E, una evolución del HBM3 que alcanza anchos de banda de 1,2 TB/s por stack. Esta tecnología es esencial para aplicaciones de IA, donde los modelos de aprendizaje profundo requieren acceso masivo a datos en paralelo. Por ejemplo, en un clúster de entrenamiento de IA, un solo servidor con GPUs NVIDIA H100 puede consumir hasta 1 TB de HBM, y Samsung ha asegurado contratos para suministrar el 50% de estos módulos en 2024. La fabricación de HBM involucra procesos de bonding híbrido, que combinan microbumps de cobre e indio para una alineación precisa a nivel de micrones, minimizando defectos y mejorando la fiabilidad térmica bajo cargas de hasta 100 W por chip.

Otra innovación clave es la adopción de EUV en la producción de lógica periférica integrada en los chips DRAM. La litografía EUV, desarrollada por ASML, utiliza longitudes de onda de 13,5 nm para patrones sub-10 nm, reduciendo el número de máscaras requeridas y el tiempo de ciclo de producción en un 15%. Samsung ha implementado EUV de alta NA (Numerical Aperture) en su línea de Pyeongtaek, lo que permite yields superiores al 90% en wafers de 12 pulgadas. Estos avances no solo bajan los costos unitarios, sino que también mitigan riesgos de seguridad en la cadena de suministro, alineándose con estándares como ISO 26262 para la integridad de datos en sistemas críticos.

Desde una perspectiva de ciberseguridad, los chips DRAM de Samsung incorporan mecanismos de encriptación hardware como AES-256 en controladores integrados, protegiendo contra ataques de side-channel como Rowhammer. Rowhammer es una vulnerabilidad que explota el acoplamiento capacitivo entre celdas adyacentes para inducir flips de bits, y Samsung ha implementado mitigaciones como Target Row Refresh (TRR), que refresca filas vulnerables de manera proactiva, reduciendo el riesgo en entornos de IA donde la integridad de datos es paramount.

Comparación Técnica con SK Hynix

SK Hynix, por su parte, ha enfocado sus esfuerzos en la optimización de HBM para el ecosistema de NVIDIA, con stacks de 12 capas que alcanzan densidades de 36 GB por módulo. Sin embargo, Samsung ha superado esta capacidad con HBM3E de 16 capas, ofreciendo 48 GB por stack y un ancho de banda de 1,4 TB/s. En términos de eficiencia energética, los chips de Samsung consumen 20% menos potencia gracias a arquitecturas de bajo voltaje (1,1 V vs. 1,2 V en competidores), lo que es crucial para centros de datos sostenibles que buscan cumplir con regulaciones como el EU Green Deal.

En el segmento de DDR5 para PCs y servidores, SK Hynix domina en módulos RDIMM (Registered DIMM) con latencias CL32, pero Samsung ha introducido variantes con ECC (Error-Correcting Code) on-die, que detectan y corrigen errores de un bit en tiempo real sin overhead de CPU. Esta característica es vital en aplicaciones de blockchain, donde la inmutabilidad de datos previene fraudes en transacciones distribuidas. Comparativamente, la tasa de errores en DRAM sin ECC puede alcanzar 1 en 10^12 bits, pero con las implementaciones de Samsung, se reduce a 1 en 10^15, alineándose con estándares NIST para criptografía post-cuántica.

En cuanto a capacidad de producción, SK Hynix opera plantas en Corea e Indonesia con una salida anual de 300.000 wafers, pero Samsung ha expandido a 450.000 wafers mediante automatización robótica y IA predictiva para mantenimiento. Algoritmos de machine learning, basados en redes neuronales convolucionales, analizan datos de sensores en tiempo real para predecir fallos en equipos de litografía, incrementando la disponibilidad en un 25%. Esta integración de IA en la fabricación representa un avance en Industria 4.0, donde la ciberseguridad se asegura mediante segmentación de redes y protocolos como OPC UA Secure.

Implicaciones Operativas y Regulatorias

El liderazgo renovado de Samsung tiene implicaciones profundas en la cadena de suministro global de semiconductores. Con la escasez de 2021-2022 aún fresca en la memoria, esta posición fortalece la resiliencia contra disrupciones geopolíticas, como las tensiones en el Estrecho de Taiwán. Operativamente, los clientes como Apple y Google beneficiarán de precios más estables, con reducciones proyectadas del 10-15% en costos de DRAM para 2025. En términos de riesgos, la concentración de mercado podría fomentar prácticas anticompetitivas, atrayendo escrutinio de reguladores como la FTC en EE.UU. y la Comisión Europea.

Desde el punto de vista regulatorio, las memorias DRAM deben cumplir con estándares ambientales como RoHS (Restriction of Hazardous Substances) y REACH, que limitan sustancias tóxicas en la producción. Samsung ha liderado en la adopción de materiales reciclados, utilizando silicio de bajo carbono en un 30% de sus wafers, reduciendo la huella de carbono en 1,5 millones de toneladas anuales. En ciberseguridad, la integración de TPM (Trusted Platform Module) en módulos DRAM asegura el arranque seguro en sistemas IoT, previniendo ataques como Spectre y Meltdown que explotan cachés compartidos.

En el contexto de IA y blockchain, el avance de Samsung acelera la adopción de edge computing. Por ejemplo, en redes blockchain como Ethereum 2.0, los nodos validadores requieren memorias de alta densidad para procesar transacciones en Proof-of-Stake, y los chips DDR5 de Samsung soportan hasta 128 GB por DIMM, facilitando la escalabilidad. Beneficios incluyen menor latencia en inferencia de IA, donde modelos como GPT-4 demandan terabytes de memoria durante el entrenamiento, y riesgos mitigados mediante redundancia en clústeres distribuidos.

Aplicaciones en Inteligencia Artificial y Blockchain

La intersección entre memorias DRAM avanzadas y IA es evidente en los aceleradores de hardware. Plataformas como Tensor Processing Units (TPUs) de Google dependen de HBM para manejar matrices de datos masivas en operaciones de multiplicación matricial. Samsung’s HBM3E ofrece un ancho de banda que soporta flujos de datos de 8192 bits por ciclo, esencial para algoritmos de deep learning que procesan billones de parámetros. En términos técnicos, la arquitectura de canal ancho reduce bottlenecks en el bus de memoria, mejorando el throughput en un 40% comparado con GDDR6.

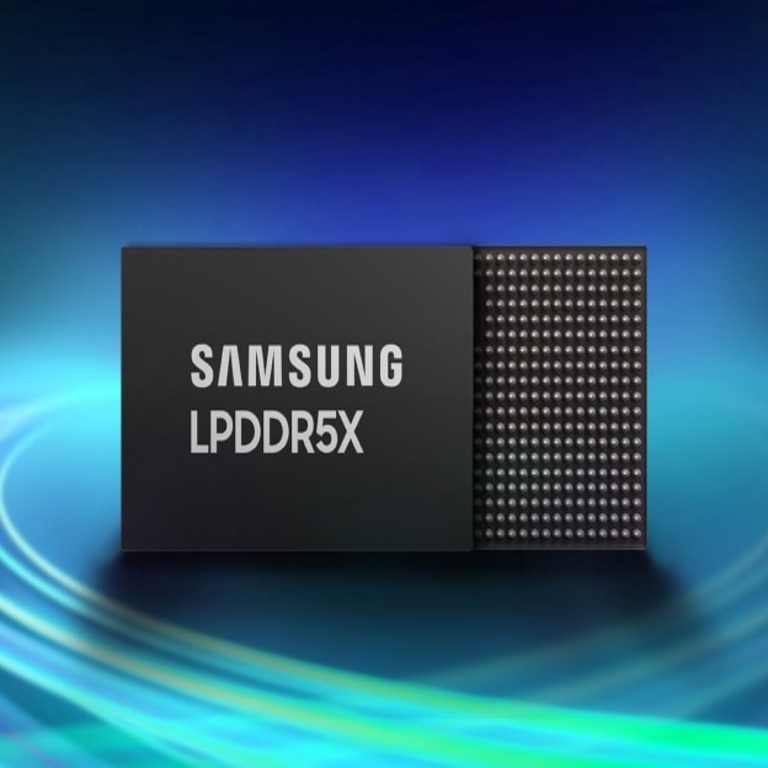

En blockchain, las memorias DRAM de alta velocidad habilitan nodos full-node que almacenan ledgers completos en RAM para validación rápida. Por instancia, en Bitcoin, un nodo requiere al menos 16 GB de DRAM para caching de UTXO (Unspent Transaction Outputs), y las variantes LPDDR5 de Samsung, con bajo consumo (0,5 W por módulo), son ideales para dispositivos móviles en wallets hardware. Además, la resistencia a ataques de denegación de servicio se fortalece con buffers de memoria protegidos por firewalls de hardware, alineados con estándares BIP-32 para derivación de claves.

Para ciberseguridad, los chips DRAM incorporan features como Secure Boot y attestation remota, permitiendo verificación de integridad en entornos cloud. En un escenario de ataque, mecanismos como memory encryption evitan fugas de datos sensibles en aplicaciones de IA federada, donde múltiples entidades comparten modelos sin exponer datos privados. Samsung’s implementación utiliza claves derivadas de PUF (Physical Unclonable Functions), que generan identificadores únicos basados en variaciones nanométricas en el silicio, resistentes a clonación.

Desafíos Futuros y Estrategias de Mitigación

A pesar de estos avances, el mercado de DRAM enfrenta desafíos como la volatilidad de precios y la competencia de tecnologías emergentes como MRAM (Magnetoresistive RAM) y ReRAM. Samsung está invirtiendo en R&D para híbridos DRAM-NVM (Non-Volatile Memory), que combinan volatilidad con persistencia para reducir latencias en cold starts de IA. Estratégicamente, alianzas con TSMC para foundry services diversifican riesgos, mientras que programas de capacitación en IA aseguran mano de obra calificada.

En mitigación de riesgos, Samsung emplea simulaciones Monte Carlo para predecir fallos en yields, utilizando modelos probabilísticos que integran variables como temperatura y radiación cósmica, que pueden inducir soft errors en altitudes elevadas. Estas simulaciones, ejecutadas en clústeres con sus propios chips, logran precisiones del 95%, optimizando diseños bajo estándares JEDEC JESD209 para robustez ambiental.

Conclusión

La recuperación del liderazgo de Samsung en el mercado de memorias DRAM marca un hito en la evolución tecnológica, impulsado por innovaciones en fabricación y optimización de rendimiento. Este posicionamiento no solo beneficia a la compañía en términos económicos, sino que también acelera avances en IA, blockchain y ciberseguridad, donde la memoria de alta velocidad es un habilitador clave. Con proyecciones de crecimiento sostenido, el sector se prepara para demandas futuras, equilibrando innovación con responsabilidad regulatoria y ambiental. Para más información, visita la Fuente original.