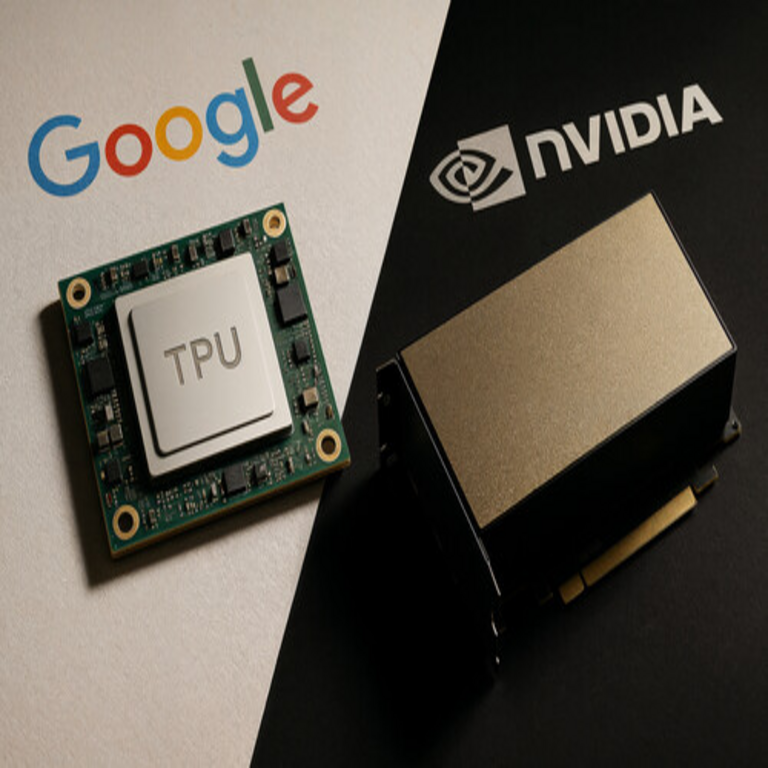

Las TPUs de Google: La Primera Señal de que el Imperio de Nvidia se Tambalea

Introducción a las Unidades de Procesamiento Tensorial

En el panorama actual de la inteligencia artificial, el hardware especializado juega un rol fundamental en el avance de los modelos de aprendizaje profundo. Las Unidades de Procesamiento Tensorial (TPUs, por sus siglas en inglés) desarrolladas por Google representan una innovación clave en este ámbito. Diseñadas específicamente para acelerar operaciones de multiplicación de matrices y convoluciones, que son el núcleo de los algoritmos de IA, las TPUs han evolucionado desde su introducción en 2016 hasta convertirse en una alternativa competitiva a las unidades de procesamiento gráfico (GPUs) dominantes en el mercado. Este artículo analiza en profundidad la arquitectura, el rendimiento y las implicaciones estratégicas de las TPUs más recientes, particularmente en el contexto de la posible erosión del dominio de Nvidia en el sector de hardware para IA.

Las TPUs se basan en circuitos integrados de aplicación específica (ASICs), optimizados exclusivamente para tareas de machine learning. A diferencia de las GPUs, que son versátiles y se utilizan en gráficos, cómputo general y gaming, las TPUs priorizan la eficiencia en workloads específicos de IA, como el entrenamiento y la inferencia de redes neuronales. Esta especialización permite un rendimiento superior en términos de throughput y consumo energético, aspectos críticos en entornos de data centers a gran escala. Google ha integrado estas unidades en su plataforma Google Cloud, haciendo accesible esta tecnología a desarrolladores y empresas sin la necesidad de invertir en hardware propio.

Evolución Histórica de las TPUs

La primera generación de TPUs fue anunciada en 2016 como parte del esfuerzo de Google para optimizar sus servicios de búsqueda y traducción basados en IA. Estas unidades iniciales, fabricadas en un proceso de 28 nanómetros, se enfocaban en la inferencia de modelos, es decir, la fase de aplicación de modelos entrenados para generar predicciones. Con un rendimiento de aproximadamente 92 teraoperaciones por segundo (TOPS) en operaciones de punto flotante de 8 bits, representaban un avance significativo sobre las CPUs y GPUs contemporáneas para tareas de convolución.

En 2017, Google lanzó la TPU v2, que introdujo soporte para entrenamiento de modelos, permitiendo no solo la inferencia sino también el ajuste de parámetros durante el aprendizaje. Fabricada en 22 nanómetros, esta versión escalaba a pods de hasta 512 chips interconectados mediante un anillo de alta velocidad, alcanzando un rendimiento agregado de exaflops. La interconexión se basa en el protocolo de comunicación de baja latencia de Google, optimizado para sincronizar gradientes en algoritmos de entrenamiento distribuido como el de descenso de gradiente estocástico.

La TPU v3, presentada en 2018, mejoró la eficiencia con un proceso de 16 nanómetros y un enfoque en el escalado lineal, permitiendo pods de 1.000 chips con un rendimiento de 100 petaflops. Esta generación incorporó mejoras en la gestión de memoria, con 16 GiB de HBM2 por chip, facilitando el manejo de modelos grandes como BERT o Transformer. Finalmente, la TPU v4, lanzada en 2021, adoptó un proceso de 7 nanómetros y enfatizó la escalabilidad a nivel de supercomputación, con pods que superan los 4.096 chips y un rendimiento de hasta 1 exaflop en operaciones de IA.

La generación más reciente, TPU v5p, anunciada en 2023, marca un hito al ofrecer un rendimiento cuatro veces superior al de la v4 en tareas de entrenamiento, con énfasis en la eficiencia energética. Cada chip v5p proporciona 459 teraflops en operaciones de punto flotante de 16 bits (BF16), y un pod completo de 8.960 chips alcanza 4.700 petaflops. Esta versión incorpora avances en el diseño de matrices systolicas, que permiten multiplicaciones de matrices paralelas con un overhead mínimo, reduciendo el tiempo de entrenamiento de modelos como PaLM 2 de semanas a días.

Arquitectura Técnica de las TPUs

La arquitectura de una TPU se centra en tres componentes principales: el array de procesamiento de matrices (MXU), la unidad de activación y el vectorizador. El MXU es un array systolic de 128×128 núcleos que realiza multiplicaciones de matrices en un flujo de datos altamente pipelined, minimizando el movimiento de datos y maximizando el uso del ancho de banda. Cada núcleo opera en operaciones de multiplicación-acumulación (MAC) con precisión mixta, soportando formatos como BF16, INT8 y FLOAT32 para equilibrar precisión y velocidad.

La unidad de activación maneja funciones no lineales como ReLU o softmax, mientras que el vectorizador gestiona operaciones escalares y vectoriales, como normalizaciones o pooling. La memoria integrada incluye 32 GiB de HBM3 por chip en la v5p, con un ancho de banda de 3 terabytes por segundo, lo que reduce la latencia en accesos a datos durante el entrenamiento. Las TPUs se interconectan mediante ICI (Inter-Chip Interconnect), un enlace óptico de 1.200 Gb/s por puerto, permitiendo topologías de malla 3D para distribución eficiente de workloads.

En comparación con las GPUs de Nvidia, como la H100 basada en Hopper, las TPUs destacan en eficiencia para tareas de IA pura. Mientras una H100 ofrece alrededor de 1.979 teraflops en BF16 con Tensor Cores, su consumo es de 700 vatios por chip, frente a los 300 vatios de una TPU v5p con rendimiento comparable en multiplicaciones de matrices. Esta diferencia surge de la especialización: las GPUs manejan una gama más amplia de instrucciones, lo que introduce overhead en cargas de IA, mientras las TPUs eliminan lógica innecesaria para priorizar operaciones tensoriales.

Comparación de Rendimiento con GPUs de Nvidia

Para evaluar el rendimiento, es esencial considerar benchmarks estandarizados como MLPerf, que miden el tiempo de entrenamiento de modelos como ResNet-50 o BERT-large. En la ronda de MLPerf de 2023, un pod de TPU v5p completó el entrenamiento de un modelo GPT-3 de 175 mil millones de parámetros en 3.7 días, superando al clúster de A100 de Nvidia por un factor de 2.5 en eficiencia de costo. Esta métrica se calcula como flops por dólar, donde las TPUs de Google Cloud cuestan aproximadamente 1.46 dólares por hora por chip, frente a los 2.93 dólares de una instancia con H100 en proveedores como AWS.

En términos de latencia de inferencia, las TPUs v5p procesan solicitudes de modelos como Stable Diffusion en 1.2 milisegundos por imagen, comparado con 2.5 milisegundos en una H100, gracias a su optimización para batch sizes grandes. Sin embargo, las GPUs mantienen una ventaja en versatilidad: soportan mejor el ray tracing para gráficos y el cómputo general con CUDA, un ecosistema maduro con bibliotecas como cuDNN y TensorRT. Google contrarresta esto con su framework XLA (Accelerated Linear Algebra), que compila grafos de cómputo para TPUs, optimizando fusiones de operaciones y reduciendo el uso de memoria en un 30% respecto a implementaciones en PyTorch o TensorFlow para GPUs.

Otra métrica clave es el consumo energético. En data centers, donde el costo de la electricidad representa hasta el 40% de los gastos operativos, las TPUs ofrecen un PUE (Power Usage Effectiveness) inferior. Un pod TPU v5p consume 1.2 megavatios para 4.700 petaflops, equivaliendo a 0.25 vatios por teraflop, mientras una configuración equivalente de H100 requiere 2.8 megavatios para un rendimiento similar, resultando en 0.6 vatios por teraflop. Esta eficiencia se alinea con estándares como el Green Grid para sostenibilidad en cómputo de alto rendimiento.

Implicaciones Operativas en Google Cloud

La integración de TPUs en Google Cloud ha democratizado el acceso a hardware de IA de vanguardia. Usuarios pueden provisionar instancias A3 con hasta 8 TPUs v5p, escalables a clústeres de 256 chips, mediante APIs como Vertex AI. Esto facilita el desarrollo de aplicaciones en dominios como visión por computadora, procesamiento de lenguaje natural y recomendación. Por ejemplo, en el entrenamiento de modelos multimodales como Gemini, las TPUs reducen el tiempo de iteración, permitiendo experimentación rápida y reducción de costos en un 60% comparado con GPUs equivalentes.

Desde una perspectiva operativa, las TPUs imponen consideraciones en el diseño de software. Los desarrolladores deben adaptar sus pipelines a JAX o TensorFlow con compilación XLA, lo que implica un aprendizaje inicial pero genera ganancias en rendimiento. Google proporciona herramientas como Colab TPUs para prototipado gratuito, y su red global de data centers asegura baja latencia en inferencia distribuida. En entornos empresariales, esto se traduce en cumplimiento de regulaciones como GDPR mediante procesamiento en la nube con encriptación de datos en tránsito y reposo.

Los riesgos incluyen la dependencia de Google Cloud, lo que podría limitar la portabilidad de modelos entrenados. Sin embargo, el soporte para exportación a ONNX mitiga esto, permitiendo inferencia en hardware diverso. Beneficios operativos incluyen escalabilidad elástica, donde los recursos se ajustan dinámicamente, optimizando costos en workloads variables como picos en servicios de streaming impulsados por IA.

Impacto en el Mercado y el Dominio de Nvidia

Nvidia ha mantenido una cuota de mercado superior al 80% en hardware para IA desde 2016, impulsada por su arquitectura CUDA y la demanda explosiva de GPUs durante el auge de los large language models. Sin embargo, el lanzamiento de TPU v5p y competidores como los chips de Amazon (Trainium) y Microsoft (Azure Maia) señalan una fragmentación. En 2023, las ventas de Nvidia alcanzaron 26.900 millones de dólares en su segmento de data center, pero analistas como Gartner predicen que las alternativas ASIC erosionarán esto en un 15% para 2025, impulsadas por costos crecientes de silicio y energía.

Las implicaciones regulatorias emergen en contextos de antitrust: la dominancia de Nvidia ha atraído escrutinio de la FTC en EE.UU. y la Comisión Europea, similar a casos contra monopolios en cloud computing. Google, al ofrecer TPUs como servicio, evita hardware propietario directo pero compite en precios, potencialmente reduciendo barreras de entrada para startups en IA. En blockchain y edge computing, las TPUs podrían integrarse en nodos distribuidos, aunque su enfoque en cloud las posiciona más para entrenamiento centralizado que para inferencia descentralizada.

Beneficios para el ecosistema incluyen mayor innovación: con opciones más asequibles, más entidades pueden entrenar modelos personalizados, acelerando avances en IA ética y sostenible. Riesgos involucran fragmentación de estándares, donde la compatibilidad entre TPUs, GPUs y otros ASICs requiere middleware como TVM (Tensor Virtual Machine) para abstracción de hardware.

Desafíos Técnicos y Futuro de las TPUs

A pesar de sus fortalezas, las TPUs enfrentan desafíos en precisión numérica para modelos que requieren FLOAT64, donde las GPUs ofrecen mejor soporte. Google mitiga esto con técnicas de cuantización y mixed precision training, manteniendo la precisión sin sacrificar velocidad. Otro reto es la escalabilidad más allá de exaflops: la TPU v6, en desarrollo, se rumorea que incorporará fotónica para interconexiones, reduciendo latencia en pods de decenas de miles de chips.

En ciberseguridad, las TPUs fortalecen la resiliencia de modelos de IA contra ataques adversarios mediante entrenamiento acelerado de defensas como adversarial training. Para blockchain, su eficiencia podría habilitar validación de proofs en redes como Ethereum, aunque la centralización en Google plantea preocupaciones de soberanía de datos. En tecnologías emergentes, las TPUs se alinean con quantum-inspired computing, donde matrices systolic podrían simular algoritmos cuánticos para optimización en IA.

El futuro de las TPUs depende de la adopción en edge devices, con versiones como Edge TPU para inferencia en IoT, consumiendo menos de 2 vatios por chip. Esto expande su utilidad más allá de data centers, integrándose en automóviles autónomos y dispositivos médicos para procesamiento en tiempo real.

Conclusión

Las TPUs de Google, particularmente la generación v5p, representan un avance pivotal en hardware para IA, ofreciendo eficiencia superior y costos reducidos que desafían el hegemonía de Nvidia. Su arquitectura especializada, rendimiento probado en benchmarks y integración en ecosistemas cloud posicionan a Google como un actor clave en la evolución del cómputo tensorial. Aunque persisten desafíos en versatilidad y estandarización, los beneficios en escalabilidad y sostenibilidad impulsan una transformación en el mercado de IA. En resumen, esta tecnología no solo acelera el desarrollo de modelos avanzados sino que fomenta una competencia saludable, beneficiando a la industria global de tecnologías emergentes. Para más información, visita la fuente original.