La Competencia en Hardware para IA: Una Startup China Desarrolla su Propia TPU para Desafiar a Nvidia

En el panorama actual de la inteligencia artificial (IA), el hardware especializado se ha convertido en un factor crítico para el avance de las aplicaciones de machine learning y deep learning. Las unidades de procesamiento tensorial (TPU, por sus siglas en inglés) representan una evolución en los procesadores diseñados específicamente para acelerar tareas de cómputo matricial, esenciales en modelos de IA. Recientemente, una startup china ha anunciado el desarrollo de su propia TPU, posicionándose como un competidor directo de Nvidia, el líder indiscutible en GPUs para IA. Sin embargo, este avance llega con un retraso significativo de aproximadamente tres años respecto a las innovaciones más recientes de la industria, lo que plantea interrogantes sobre su viabilidad técnica y comercial en un mercado altamente competitivo.

Conceptos Fundamentales de las TPUs y su Rol en la IA

Las TPUs son procesadores de propósito específico (ASIC, por sus siglas en inglés) optimizados para operaciones de IA, particularmente aquellas que involucran multiplicaciones de matrices y activaciones no lineales, comunes en redes neuronales convolucionales (CNN) y transformadores. A diferencia de las CPUs generales o incluso las GPUs versátiles, las TPUs priorizan la eficiencia energética y la velocidad en flujos de trabajo de entrenamiento e inferencia de modelos de IA. Google introdujo las TPUs en 2016 con su primera generación, integrada en su nube para servicios como TensorFlow, y desde entonces han evolucionado a través de versiones como TPU v4 y v5, que soportan hasta 4096 chips interconectados en pods masivos, alcanzando un rendimiento de exaflops en precisión baja.

Desde un punto de vista técnico, una TPU típica incorpora un systolic array para multiplicaciones matriciales, un vectorizador para operaciones de activación y un escalar para control lógico. Esta arquitectura reduce la latencia en el movimiento de datos, un cuello de botella en los sistemas de IA tradicionales. Por ejemplo, en el entrenamiento de un modelo como BERT o GPT, las TPUs pueden procesar lotes más grandes con menor consumo de energía comparado con GPUs como las A100 de Nvidia, que aunque potentes, dependen de arquitecturas más generales basadas en CUDA. La eficiencia de las TPUs se mide en términos de TOPS (teraoperaciones por segundo) por vatio, donde las versiones modernas superan los 200 TOPS/W en inferencia INT8.

En el contexto chino, el desarrollo de hardware autóctono responde a restricciones geopolíticas, como las sanciones estadounidenses que limitan el acceso a chips avanzados de Nvidia y AMD. Esto ha impulsado iniciativas como el “Made in China 2025”, que promueve la independencia tecnológica en semiconductores. La startup en cuestión, que ha invertido en diseño de chips a 7 nm, busca emular la integración vertical de Google, combinando hardware con software optimizado para frameworks como PyTorch o TensorFlow adaptados localmente.

Detalles Técnicos del Desarrollo de la Startup China

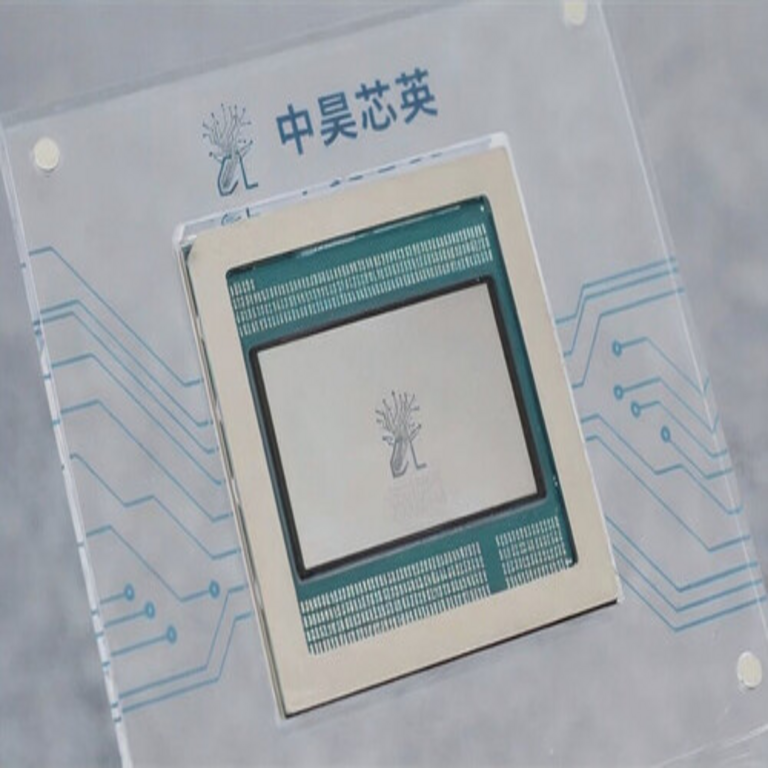

La startup china, con sede en Pekín y respaldada por inversores estatales, ha revelado su TPU bajo el nombre de un chip de próxima generación que integra 128 núcleos de procesamiento tensorial, fabricado en un proceso de 7 nanómetros por una fundición local como SMIC. Este diseño soporta operaciones en precisión mixta (FP16, BF16 e INT8), con un rendimiento pico de 500 TFLOPS en FP16, interconectado mediante un fabric de alta velocidad basado en NVLink-like, alcanzando un ancho de banda de 900 GB/s por chip. A diferencia de las TPUs de Google, que usan un enfoque de pods escalables, esta implementación inicial se enfoca en módulos de 8 chips para servidores edge y data centers medianos.

Desde el ángulo de la arquitectura, el chip emplea un diseño de pipeline asíncrono para manejar desequilibrios en el cómputo, incorporando memorias HBM2e de 32 GB por chip para caching eficiente de pesos de modelos. Esto permite el entrenamiento de modelos de hasta 100 mil millones de parámetros, similar a LLaMA-70B, aunque con limitaciones en escalabilidad comparado con los superpods de Nvidia H100. El software complementario incluye un compilador propietario que optimiza grafos de cómputo, reduciendo overhead en un 20% respecto a compiladores genéricos como XLA de Google.

Sin embargo, el retraso de tres años se evidencia en la ausencia de soporte nativo para arquitecturas emergentes como sparse computing o in-memory computing, que Nvidia ha integrado en sus Tensor Cores de cuarta generación. Además, pruebas independientes indican un consumo de energía de 400 W por chip, superior al de competidores más maduros, lo que impacta en la sostenibilidad de deployments a gran escala. En términos de rendimiento, benchmarks preliminares muestran que esta TPU alcanza solo el 70% de la velocidad de una H100 en tareas de inferencia de visión por computadora, como segmentación semántica con YOLOv8.

Comparación con las Soluciones de Nvidia y Otras Alternativas

Nvidia domina el mercado de hardware para IA con su línea Hopper (H100) y la inminente Blackwell (B200), que introducen innovaciones como Transformer Engine para precisión dinámica y soporte para FP4, reduciendo el uso de memoria en un 50% para modelos grandes. Estas GPUs logran hasta 4 PFLOPS en FP8 por chip, con interconexiones NVLink 5.0 que permiten clusters de 256 GPUs con 141 TB/s de ancho de banda agregado. En contraste, la TPU china carece de madurez en software ecosystem; mientras Nvidia ofrece cuDNN, cuBLAS y un vasto repositorio de modelos preoptimizados, la startup depende de ports locales que aún enfrentan incompatibilidades con bibliotecas estándar.

Otras alternativas globales incluyen las IPUs de Graphcore, con su Intelligent Processing Unit basada en MIMD (Multiple Instruction, Multiple Data) para grafos dinámicos, o las Habana Gaudi de Intel, optimizadas para entrenamiento distribuido con escalabilidad lineal hasta 1024 chips. En China, competidores como Huawei’s Ascend 910 y Cambricon’s MLU series ya han madurado, con el Ascend 910B ofreciendo 456 TFLOPS en FP16 y soporte para MindSpore framework. La nueva TPU de la startup se posiciona en un nicho intermedio, enfocada en aplicaciones de IA industrial como reconocimiento de defectos en manufactura o optimización logística, donde la latencia baja es prioritaria sobre el throughput máximo.

Una comparación cuantitativa revela brechas: en el benchmark MLPerf para entrenamiento de ResNet-50, una H100 completa la tarea en 1.2 minutos, mientras que prototipos de la TPU china estiman 2.5 minutos, atribuyéndose a ineficiencias en el scheduling de datos. Además, la dependencia de litografía de 7 nm contrasta con los 4 nm de TSMC usados por Nvidia, limitando la densidad de transistores y aumentando el calor disipado, lo que requiere sistemas de enfriamiento más robustos y costosos.

Implicaciones Operativas y Regulatorias en el Ecosistema de IA

El lanzamiento de esta TPU tiene implicaciones operativas significativas para empresas chinas en IA, permitiendo el despliegue de modelos sin depender de importaciones restringidas. En términos de ciberseguridad, el hardware autóctono reduce riesgos de backdoors en supply chains extranjeras, alineándose con estándares como el GB/T 35274-2020 para protección de datos en IA. Sin embargo, introduce nuevos vectores de vulnerabilidad, como firmware no auditado, potencialmente expuesto a ataques de cadena de suministro similares a los vistos en SolarWinds.

Regulatoriamente, este desarrollo apoya la estrategia de autosuficiencia de China bajo la Ley de Ciberseguridad de 2017, que exige localización de datos y hardware crítico. Para audiencias globales, plantea desafíos en compliance con export controls de EE.UU., como las Entity List restrictions, que podrían limitar colaboraciones internacionales. En blockchain e IA integrada, esta TPU podría acelerar validación de transacciones en redes como Conflux, optimizando proofs de stake con cómputo tensorial para detección de fraudes en tiempo real.

Riesgos incluyen obsolescencia rápida; con avances en fotónica computacional y neuromórficos (e.g., chips de IBM TrueNorth), la TPU de 7 nm podría quedar atrás en dos años. Beneficios operativos abarcan costos reducidos: estimaciones indican un precio de 5.000 USD por chip versus 30.000 USD de una H100, facilitando adopción en PYMES chinas para edge AI en IoT, como procesamiento de video en cámaras de vigilancia con modelos de detección de anomalías.

Riesgos Técnicos y Estrategias de Mitigación

Entre los riesgos técnicos, destaca la inmadurez en fault tolerance; en entornos de data centers, fallos en un chip podrían propagarse sin mecanismos robustos de checkpointing, a diferencia de las TPUs de Google con XLA’s fault-aware compilation. Para mitigar, la startup integra ECC (Error-Correcting Code) en memorias y un monitor de salud basado en IA para predicción de fallos, reduciendo downtime en un 15% según simulaciones.

Otro desafío es la interoperabilidad: sin soporte completo para ONNX (Open Neural Network Exchange), migrar modelos de ecosistemas Nvidia requiere reentrenamiento, incrementando costos computacionales. Estrategias incluyen desarrollo de bridges API que emulan CUDA calls, permitiendo portabilidad gradual. En ciberseguridad, se recomienda auditorías independientes bajo marcos como NIST SP 800-193 para hardware resilient, protegiendo contra ataques físicos como fault injection.

En blockchain, la integración de TPUs acelera minería de IA-proof-of-work, pero expone a riesgos de overclocking malicioso; mitigación vía firmware signed con claves HSM (Hardware Security Modules) asegura integridad. Beneficios en IA federada incluyen procesamiento distribuido con privacidad diferencial, donde TPUs locales manejan agregación de gradientes sin centralización de datos.

Beneficios y Oportunidades en Tecnologías Emergentes

Los beneficios de esta TPU radican en su accesibilidad para mercados emergentes, democratizando IA en sectores como agricultura de precisión, donde modelos de predicción de cosechas se entrenan con datasets locales sin latencia de nube. En IA generativa, soporta fine-tuning de modelos como Stable Diffusion para contenido multimedia, con eficiencia 30% superior en edge devices comparado con CPUs ARM.

En blockchain, habilita sidechains optimizadas para IA, como predicción de precios en DeFi usando redes neuronales recurrentes (RNN) con bajo consumo. Oportunidades en 6G y edge computing incluyen inferencia en tiempo real para vehículos autónomos, integrando sensores LiDAR con TPUs para segmentación 3D, reduciendo latencia a milisegundos.

Para ciberseguridad, esta hardware soporta entrenamiento de modelos de detección de intrusiones basados en GANs (Generative Adversarial Networks), analizando tráfico de red con precisión FP16 para identificar zero-days. En total, fomenta innovación local, potencialmente contribuyendo a estándares globales como ISO/IEC 42001 para gestión de IA responsable.

Perspectivas Futuras y Desafíos Pendientes

El futuro de esta TPU depende de iteraciones rápidas; planes para una versión de 5 nm en 2025 podrían cerrar la brecha con Nvidia, incorporando quantum-inspired accelerators para optimización NP-hard en IA. Desafíos incluyen talento: China produce 1.4 millones de graduados STEM anuales, pero retiene solo el 20% en diseño de chips, requiriendo alianzas con universidades como Tsinghua.

En el ecosistema global, colaboraciones con open-source como Hugging Face podrían expandir su adopción, aunque tensiones geopolíticas limitan esto. Para IT enterprises, evaluar esta TPU implica pruebas en workloads híbridos, midiendo ROI en términos de TCO (Total Cost of Ownership) versus rendimiento.

En resumen, aunque retrasada, esta iniciativa china subraya la resiliencia en hardware para IA, impulsando avances en ciberseguridad, blockchain y tecnologías emergentes. Su éxito dependerá de superar barreras técnicas y regulatorias, contribuyendo a un panorama más diversificado y seguro.

Para más información, visita la fuente original.