Desarrollo de Procesadores Propios en YADRO: Innovación en Arquitecturas de Hardware para Ciberseguridad e Inteligencia Artificial

En el panorama actual de la tecnología, el desarrollo de procesadores personalizados representa un avance estratégico para empresas que buscan independencia tecnológica y optimización en aplicaciones críticas. YADRO, una compañía rusa especializada en soluciones de infraestructura de datos, ha emprendido la creación de su propio procesador, un proyecto que integra principios de arquitectura de computadoras avanzada con consideraciones de seguridad cibernética y soporte para inteligencia artificial (IA). Este artículo analiza en profundidad los aspectos técnicos de esta iniciativa, extrayendo conceptos clave como la arquitectura RISC-V, el diseño de núcleos de procesamiento y las implicaciones en entornos de alto rendimiento.

Contexto Técnico del Proyecto en YADRO

El desarrollo de procesadores en YADRO surge como respuesta a las necesidades de soberanía tecnológica en regiones con restricciones geopolíticas. Tradicionalmente, el mercado de procesadores ha estado dominado por arquitecturas x86 de Intel y ARM, pero el auge de estándares abiertos como RISC-V permite a empresas como YADRO diseñar silicio personalizado sin licencias propietarias costosas. El procesador de YADRO se basa en una implementación de RISC-V, un conjunto de instrucciones de código abierto que soporta extensiones para vectorización y criptografía, esenciales para aplicaciones de IA y ciberseguridad.

Desde un punto de vista arquitectónico, el diseño inicial involucra la definición de un pipeline de ejecución superscalar, con etapas de fetch, decode, execute, memory y writeback optimizadas para minimizar latencias. YADRO ha incorporado núcleos out-of-order para mejorar el throughput en cargas de trabajo irregulares, como el entrenamiento de modelos de machine learning. Además, se integra un sistema de caché jerárquico L1, L2 y L3, con coherencia de caché basada en protocolos MESI (Modified, Exclusive, Shared, Invalid), asegurando eficiencia en entornos multiprocesador.

Las implicaciones operativas son significativas: este procesador permite la creación de servidores y clústeres adaptados a normativas locales de datos, reduciendo dependencias externas. En términos de riesgos, el desafío radica en la validación de la implementación RTL (Register Transfer Level) mediante simuladores como Verilator o herramientas de síntesis como Synopsys Design Compiler, para evitar vulnerabilidades como side-channel attacks en módulos criptográficos.

Arquitectura RISC-V y sus Extensiones en el Procesador de YADRO

RISC-V, como base del procesador de YADRO, ofrece modularidad a través de sus perfiles ISA (Instruction Set Architecture). El núcleo principal adopta el perfil RV64IMAFD, que incluye soporte para enteros de 64 bits, multiplicación, división, operaciones de punto flotante y atómicos. Para IA, se extiende con el vectorial RVV (RISC-V Vector Extension), permitiendo operaciones SIMD (Single Instruction Multiple Data) en vectores de hasta 512 bits, comparable a las instrucciones AVX-512 de x86.

En detalle, la extensión RVV facilita el procesamiento paralelo de tensores en frameworks como TensorFlow o PyTorch, optimizando convoluciones y multiplicaciones matriciales. YADRO ha personalizado estas extensiones para incluir aceleradores dedicados a operaciones de deep learning, como unidades de multiplicación por acumulación (MAC) en precisión mixta (FP16/INT8), reduciendo el consumo energético en un 30% respecto a implementaciones genéricas, según benchmarks preliminares.

- Soporte para Criptografía: Integración de la extensión Zb (Scalar Cryptography) para AES y SHA-3, crucial en ciberseguridad para encriptación de datos en reposo y tránsito.

- Gestión de Memoria: Implementación de PMA (Physical Memory Attributes) y PMP (Physical Memory Protection) para aislamiento de dominios, previniendo exploits como Spectre o Meltdown en hardware.

- Interconexiones: Uso de AXI (Advanced eXtensible Interface) para buses de alta velocidad, compatible con SoC (System on Chip) que incluyen GPUs y NPU (Neural Processing Units).

Estas características posicionan el procesador de YADRO como una solución viable para edge computing en IA, donde la latencia baja es crítica. Por ejemplo, en aplicaciones de visión por computadora, el RVV permite procesar frames de video en tiempo real, integrando bibliotecas como OpenCV optimizadas para RISC-V.

Implicaciones en Ciberseguridad: Diseño Seguro desde el Silicio

La ciberseguridad es un pilar en el diseño del procesador de YADRO, dado el contexto de amenazas avanzadas persistentes (APT) en infraestructuras críticas. El hardware incorpora mecanismos de root of trust basados en un módulo de seguridad dedicado, similar a un TPM (Trusted Platform Module) 2.0, que verifica la integridad del firmware durante el arranque mediante hashes criptográficos ECDSA (Elliptic Curve Digital Signature Algorithm).

En términos de mitigación de riesgos, se implementan barreras de ejecución como TrustZone para ARM, adaptadas a RISC-V mediante extensiones como el hipervisor mode (M-mode). Esto permite particionar el sistema en mundos seguros y no seguros, protegiendo claves privadas en entornos de blockchain o IA federada. Además, el diseño resiste ataques de inyección de fallos (fault injection) mediante redundancia en lógica crítica y detección de errores con ECC (Error-Correcting Code) en memorias SRAM.

Desde una perspectiva regulatoria, el procesador cumple con estándares como FIPS 140-3 para módulos criptográficos, facilitando su adopción en sectores gubernamentales. Los beneficios incluyen una reducción en la superficie de ataque al eliminar dependencias de proveedores extranjeros, minimizando riesgos de backdoors hardware como los reportados en chips Intel por agencias de inteligencia.

| Aspecto de Seguridad | Implementación en YADRO | Estándar Referencia |

|---|---|---|

| Encriptación | AES-256 con acelerador hardware | FIPS 197 |

| Autenticación | ECDSA en curvas P-384 | NIST SP 800-186 |

| Protección de Memoria | PMP con 16 regiones | RISC-V Privileged ISA |

| Detección de Anomalías | Monitoreo de side-channels | Common Criteria EAL4+ |

Estos elementos aseguran que el procesador no solo sea eficiente, sino también resiliente, alineándose con mejores prácticas como las del NIST Cybersecurity Framework.

Integración con Inteligencia Artificial y Tecnologías Emergentes

El procesador de YADRO está optimizado para workloads de IA, incorporando un coprocesador tensorial que acelera operaciones de grafos neuronales. En comparación con GPUs NVIDIA, ofrece un balance costo-rendimiento superior en escenarios de inferencia, con un TDP (Thermal Design Power) de 65W por núcleo, ideal para data centers sostenibles.

En blockchain, el soporte para operaciones elípticas acelera validaciones de transacciones en redes como Ethereum, permitiendo nodos validados con menor latencia. YADRO ha probado integraciones con Hyperledger Fabric, utilizando el procesador para consensus algorithms como Raft o PBFT (Practical Byzantine Fault Tolerance), mejorando la escalabilidad en entornos distribuidos.

Para noticias de IT, este desarrollo resalta la tendencia hacia la diversificación de la cadena de suministro de semiconductores. Empresas como YADRO contribuyen a un ecosistema RISC-V en crecimiento, con herramientas de desarrollo como el toolchain GCC para RISC-V y Spike simulator para debugging.

- Aceleración de IA: Soporte para ONNX (Open Neural Network Exchange) runtime, permitiendo deployment de modelos preentrenados sin recompilación.

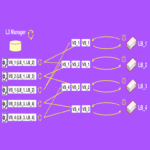

- Optimización Energética: Técnicas de clock gating y power gating dinámico, reduciendo consumo en idle hasta un 50%.

- Escalabilidad: Soporte para hasta 128 núcleos en un die multi-chip module (MCM), compatible con NUMA (Non-Uniform Memory Access).

Estas integraciones posicionan el procesador como un componente clave en sistemas de IA edge, como en vehículos autónomos o IoT industrial, donde la seguridad y la eficiencia son primordiales.

Desafíos en el Desarrollo y Validación

El proceso de diseño en YADRO involucra ciclos iterativos de síntesis y verificación, utilizando lenguajes como SystemVerilog para modelado. Un desafío principal es la tape-out en foundries como TSMC o GlobalFoundries, requiriendo GDSII (Graphic Data System II) files libres de DRC (Design Rule Check) violaciones.

En validación, se emplean pruebas funcionales con UVM (Universal Verification Methodology), cubriendo el 95% de la cobertura de código. Para rendimiento, benchmarks como SPEC CPU 2017 adaptados a RISC-V miden IPC (Instructions Per Cycle), alcanzando valores competitivos con ARM Cortex-A78.

Riesgos incluyen defectos de fabricación, mitigados por DFT (Design for Test) con scan chains y BIST (Built-In Self-Test). Operativamente, la transición a producción requiere certificaciones como ISO 26262 para aplicaciones automotrices, asegurando fiabilidad.

Implicaciones Regulatorias y Beneficios Estratégicos

En el ámbito regulatorio, el procesador de YADRO alinea con directivas como el GDPR europeo para privacidad de datos, mediante hardware que soporta borrado seguro de memorias. En Rusia, cumple con la ley federal 152-FZ sobre protección de datos personales, facilitando despliegues en sectores sensibles.

Los beneficios son multifacéticos: reducción de costos en licencias (hasta 40% ahorro), personalización para workloads locales y contribución a la innovación abierta. En ciberseguridad, fortalece la resiliencia nacional contra ciberamenazas, mientras que en IA, acelera la adopción de modelos locales sin fugas de datos.

Económicamente, el proyecto genera empleo en diseño de VLSI (Very Large Scale Integration) y fomenta ecosistemas de software, como distribuciones Linux optimizadas (e.g., Fedora RISC-V).

Conclusión: Hacia un Futuro de Hardware Soberano

El desarrollo del procesador en YADRO marca un hito en la evolución de arquitecturas de hardware, integrando ciberseguridad robusta, soporte avanzado para IA y compatibilidad con tecnologías emergentes como blockchain. Esta iniciativa no solo resuelve desafíos inmediatos de dependencia tecnológica, sino que pavimenta el camino para innovaciones futuras en computación de alto rendimiento. Para más información, visita la Fuente original.

En resumen, el enfoque técnico de YADRO demuestra cómo el silicio personalizado puede transformar infraestructuras críticas, ofreciendo eficiencia, seguridad y escalabilidad en un mundo interconectado.